최근 Germanium은 Silicon으로 이루어진 반도체 디바이스의 대체 물질로 생각되고 있다. 실리콘으로 이루어진 기존 반도체 디바이스는 scale down(크기 작게하기)이 점점 이뤄짐에 따라 한계에 부딪혔기 때문이다. 크기를 줄이는 이유는 속도를 빠르게 하고 , 에너지 효율을 높이기 위해서다.

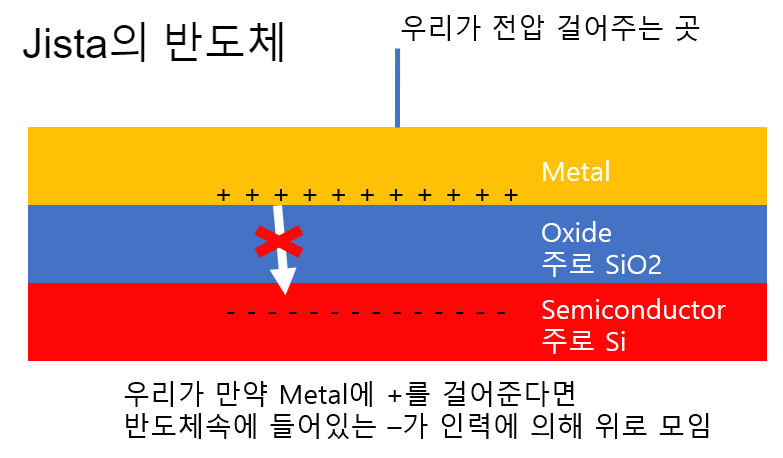

먼저 MOS 구조에 대해 간단히 알려주자면 Metal에 우리가 원하는 voltage를 걸어주고 Oxide는 전자가 흐르지 않도록 막아준다. Semiconductor은 Voltage의 양에 따라 전하가 모일수도 있고 흩어질 수도 있다. 반도체를 통해 전하를 저장하기도, 지우기도 하기 때문에 우리는 여러 제품들의 정보를 저장할수도, 지울수도 있다. USB나 컴퓨터 속에 들어있는 RAM을 생각하면 편한데 만약 전자 3개는 PPT 파일 1개와 동일하다면(사과1개 100원느낌) semiconductor에 전자 3개를 유도했을 때 USB나 RAM안에 PPT 파일 1개가 저장되는 것이다. 사과 1개가 100원의 값어치라면 100원이 있을 때 사과 한개를 언제든 구할 수 있는 것이다. 전자가 3개 있다면 우리는 그 전자의 개수를 세서 어떤 파일이 있는지 알 수 있다.

전하 유도 및 저장이 가능해서 우리는 MOS 구조를 쓴다. 위 그림은 정말 간단하게 MOS를 표현한 것이다. 위 그림을 통해서는 한가지만 기억하면 된다. Metal에 +또는 -를 걸어주면 Semiconductor에는 Metal과 반대 부호의 charge가 유도된다는 것. Oxide는 Metal또는 semiconductor속에 있는 전하가 움직이지 못하도록 막아주는 것!

만약 위 그림에서 +전하가 Oxide를 지나 Semiconductor쪽으로 가게되면 어떨까?

그러면 기껏 유도해서 모아둔 -들이 +와 합쳐져서 (+1) + (-1) = 0 을 이뤄 총 전하량은 0이 될 것이다. 그러면 아무것도 Metal에 전압을 안걸어준 상태와 같기 때문에 우리의 목표인 전하 저장을 달성하지 못한다. MOS의 장점은 다시한번 말하지만 우리가 원하는 만큼 전하를 유도한 뒤 저장할 수 있다는 것이다.

하지만 최근 반도체 디바이스의 크기를 무리하게 줄임에 따라 Oxide층이 너무 얇아져서 전자가 tunneling하는 현상이 일어나고 있다. Tunneling은 한마디로 얇은 벽을 전자가 쏙 하고 넘어 가는 것이다.

Oxide층은 강과 같은데 강의 폭이 넓으면 그 강을 사람이 지나가기 힘들겠지만 강이 좁으면 쇽 하고 넘어가는 것과 같다. 물론 수영 잘하는 사람이 넓은 강을 넘어가는 것처럼 Oxide층이 두꺼워도 넘어가는 전자가 아주 조금 있다. Oxide층이 얇아질수록 이 벽을 넘어가는 전자의 수는 기하급수적으로 늘어난다. 그래서 우리가 원하는 수만큼의 전하 저장이 안되는 것이다. 통제불능! 이를 누설전류라고 부른다.

그래서 요즘에는 이를 극복하기 위해 Germanium을 연구하고 있다. Ge는 실리콘보다 hole과 electron의 mobility가 크고(-와 +가 빠르게 움직임 LTE세상!) Si위에서 잘 자라기 때문이다.

반도체 디바이스의 크기를 줄이는 이유가 속도를 빠르게 하기 위해선데 크기를 줄이면 누설전류가 많이 생긴다. 하지만 애초에 전하의 움직임이 빠른 애들이라면 어떨까? 그렇다면 크기를 더 크게 해도 전하의 속도가 실리콘과 비슷하거나 더 빠를 것이다. 그래서 각광받는 것이 Ge다. 보통 반도체는 Si위에 물질을 증착하는데(제일 싸서), Ge는 lll lV 반도체물질 보다도 Si위에서 잘 자란다. 정말 반도체계의 유망주인데 문제가 하나 있다.

Ge위에 Oxide층을 뭐로 해야 Si처럼 좋은 전기적 특성이 나오는 지 고민이다. 실리콘은 그냥 산소만 닿으면 SiO2를 형성했고(노력이 필요없어) Metal/SiO2/Si 구조는 매우 좋은 전기적 특성을 보여서 우리 세상에 널리 쓰이고 있다. 하지만 Ge는 산소와 닿으면 GeO2만 형성하는 것이 아니라 GeOx 같은 불안정 물질을 만들어버린다. 이 GeOx는 심지어 물에도 녹는다…이런 물질을 실전에 투입했다가 공기중에 떠있는 수증기만 닿아도 순식간에 녹아버린다. 실전 투입하지도 못한다. 그래서 Ge관련 연구들은 대부분 Ge와 파트너를 이룰 Oxide층 연구가 많다.

AlO2나 LaTaON CeO2 HfTiO와 같은 물질들이 연구되어 Ge와 준수한 파트너 관계를 이뤘다고 보고됐다. 이도 모자라 Nitridation을 해보았는데 질소를 넣어줄 경우 GeON이나 AlON 같은 물질을 형성해서 더욱 더 좋은 결과를 내었다. 심지어 어떤 연구는 HfTiO를 Oxide층으로 하고 Ge 와 HfTiO 사이에 Y2O3를 passivation layer로 넣어 결과를 내었다. Passivation layer은 주로 Ge와 반응하지 않고 Ge의 diffusion을 막아서 GeOx가 형성되지 않도록 억제하는 층이다. Ge와 Oxide층을 붙어있게 했다가 얘네들이 반응하면 GeOx 생겨서 전기적 특성이 망하니까 중간에 반응안하는 barrier를 놔둔다고 보면 된다.

출처 : Wide-bandgap high- as passivating interlayer for enhancing the electrical properties and high field reliability of n-Ge MOSCAP with high k HfTiO gate dielectric

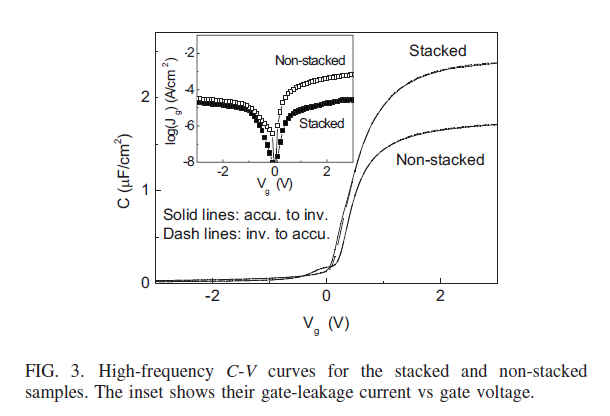

주로 이러한 CV 그래프를 통해 전기적 특성을 알아보는데 Stacked가 좋은거고 Non-stacked가 나쁜거다. Stacked는 passivation layer을 놔둔 샘플, Non-stacked 는 passivation layer을 놔두지 않은 샘플이라고 보면 된다. CV 커브는 가파를수록 좋고 C가 높을수록 좋다. 왼쪽 위 작은 그래프는 누설전류를 나타낸 그래프인데 누설전류는 낮을수록 좋다. 보면 Stacked 같은 경우 Non-stacked 보다 낮은 누설전류를 보인다. 그만큼 GeOx같은 불순물이 안생겼고 Oxide층이 자기 역할을 잘 한다는 뜻이다.

도움이 되셨다면 공감버튼이나 댓글 부탁드려요~

'공대 대학원 생활 & 반도체 지식' 카테고리의 다른 글

| [취준생 반도체 면접 준비] 면접 기출에 꼭 나오는 MOSFET 반도체 8대 공정 쉽게 설명해드립니다. (13) | 2019.04.29 |

|---|---|

| 반도체 기초 공부 :: pn접합(pn junction) depletion region 공핍영역에 대해 (3) | 2019.04.02 |

| [공대 대학원 생활]주제를 잡는다면 첫 논문이 중요하다. (0) | 2019.03.18 |

| [대학원 논문]XPS 그래프를 볼 때 알아야할 것들 (35) | 2019.03.08 |

| [대학원생 고민,알았으면 좋았을 것]공대 대학원생 인건비가 팍 줄어들었다... (3) | 2019.03.05 |