지난 번 포스팅에서는 gate 물질의 변천사, 결국 gate 물질로 metal을 쓰게된 이유에 대해 다뤄봤는데요. 오늘 다뤄볼 주제는 Fermi level pinning effect입니다. 한글로 번역하면 페르미 준위 고정 현상.

● Fermi level pinning의 정의

정의부터 알아볼까요? 말로 하면 간단해요. 반도체 물질, 예를 들어 Silicon을 metal과 접합시켰을 때 발생하는데요. surface state 때문에 Si의 Ef(fermi level)이 neutral level에 고정되려합니다. 이로 인해 metal의 work function과 관계 없이 schottkey barrier가 생겨, 양방향으로 전자가 흐르는 것이 아닌 단방향으로만 전자가 흐르게 됩니다.

● 나도 학부때 이해 못했어

처음 보면 뒤로가기 누르고 싶을 겁니다. 혹은 이 문장만 20~30번 읽던가. 저 학부때도 이거 이해 절대 못했습니다. 목표는 오늘 100% 이해하는거 아님. 계속 반복해서 보다가 어느 순간 아 ㅁㅊ 이게 그 소리구나! 하고 이해하는 거임. 10번은 넘게 봐야돼요. 그 정도로 설명이 개떡같아요.

● Surface state, interface state란 무엇인가?

이해를 하려면 일단 surface state가 뭔지부터 알아야합니다.

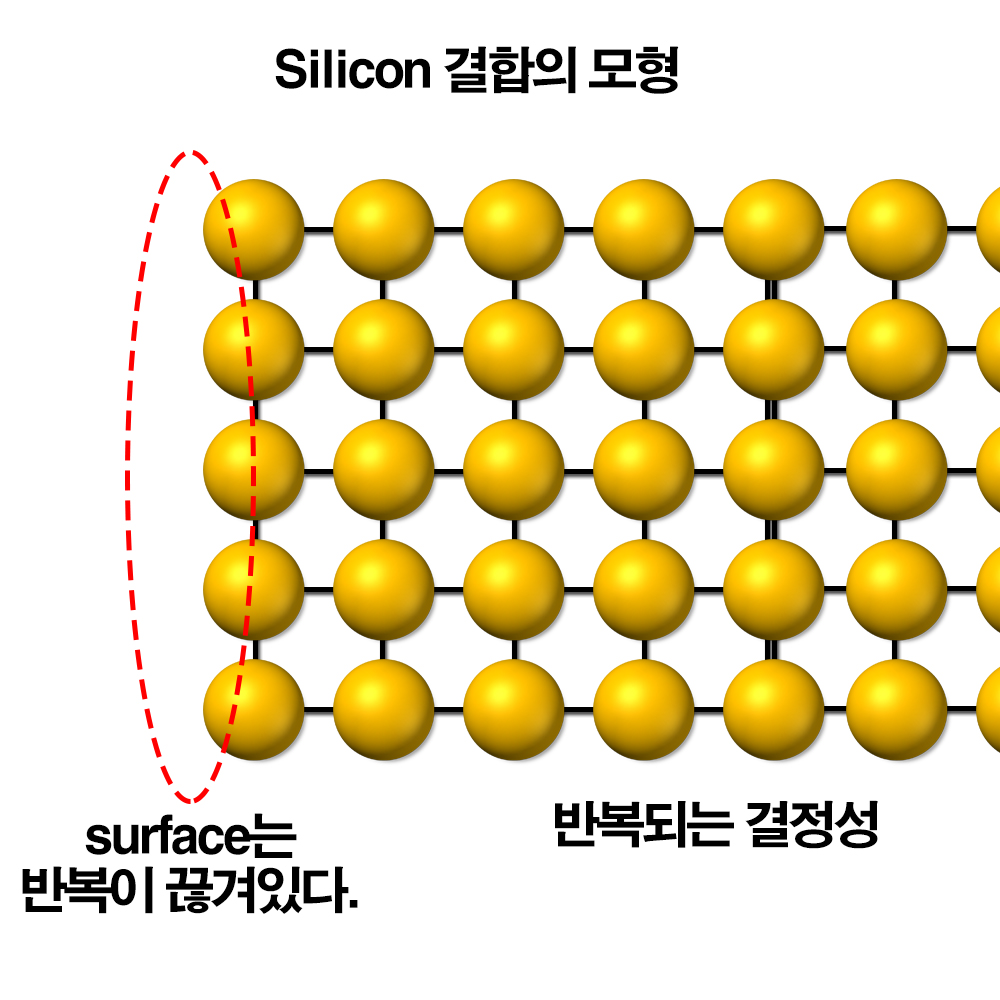

surface state는 표면 상태입니다. 그림을 일단 보시죠.

Silicon 원자가 쭈욱 나열되어있어요. 근데 Si가 무한하게 쭉 나열되어있을까요? 끝이 있습니다. 그 끝의 이름이 뭐야? surface, 즉 표면입니다. 반대로 중앙쯤은 bulk라고 불러요.

bulk, 중간을 보시면 Si끼리 잘 결합되어있습니다. 아주 octat rule을 잘지키면서요. 결정성이 유지되고 반복됩니다. ligand, 팔이 4개씩 달려있죠.

하지만 표면을 보세요. 하나씩 결합을 못했죠? Si만 고려했을 때 ligand가 3개씩 있습니다. 표면은 bulk와 다르게 반복성이 깨집니다. 결정성이 깨집니다.

앞사람 어깨 손을 시켜봐요. 뒤에 애들(bulk)은 앞사람한테 손 잘 올리죠? 근데 맨 앞 사람은?? 손 올릴 때가 없어요. 무릎에 올립니다. 왜? 맨 앞사람은 surface니까. 어떤 물질이든 결국 끝이 있단 말이야. 이 끝이 surface고, 중간과는 다른 특성을 보입니다.

'bulk와 다른 surface만의 상태다'해서 surface state라고 부릅니다. 이 surface가 다른 물질과 결합하면? interface를 형성하겠죠. 마찬가지로 interface에서는 bulk와 다른 상태일겁니다. 왜? Si끼리 결합한 것이 아니라 다른 물질과 결합한거니까! 그래서 다른 물질과 결합했을 때는 surface state가 아닌 interface state라고 부릅니다.

Surface state든 Interface state든 표면의 Silicon은 Silicon이 아닌 다른 물질과 결합한 상태입니다. Si끼리 있을 때나 conduction band와 valence band 사이를 일컫는 bandgap에 전자가 존재할 수 없는거지, 다른 애들이랑 섞인 Si은 bandgap 내부에 새로운 energy level을 만들어 냅니다. 극단적으로 말할게요. Si 표면은 bandgap이 없습니다. 중간중간 전자가 존재할 수 있는 trap level이 있습니다.

Si 표면의 bandgap = 0eV라는 뜻은 아니구요. bandgap안에서는 원래 전자가 존재할 수 없잖아요. 근데 Si 표면에서는 trap level들이 많아 전자가 존재할 수 있다는 것을 말하고자 했습니다.

● Suraface state 유무에 따른 band structure 차이

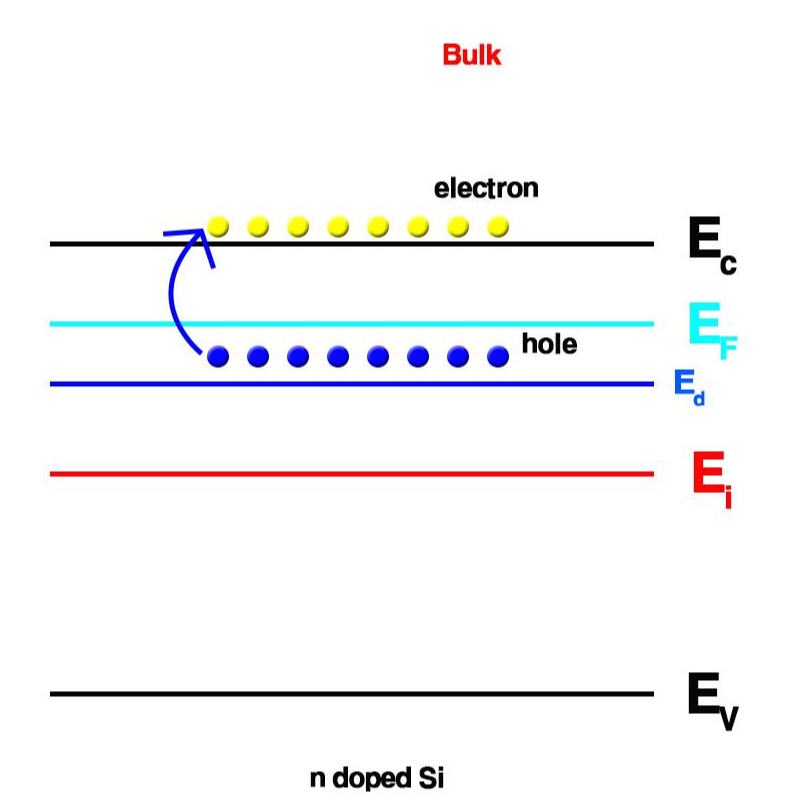

N type doping한 Si의 band structure을 예시로 볼게요. 원래라면 Ef에서 있던 electron들이 conduction band로 깡충해서 올라갔기때문에 전자들은 Ec 위에서 자유롭게 놀고있을 겁니다. 그리고 중성입니다. donor level에 hole을 남겨놓고 electron이 올라갔으니깐요. fermi level은 hole과 electron의 위치의 중간쯤 위치합니다. +와 -의 사이. 즉 중성이 어디인지를 나타냅니다.

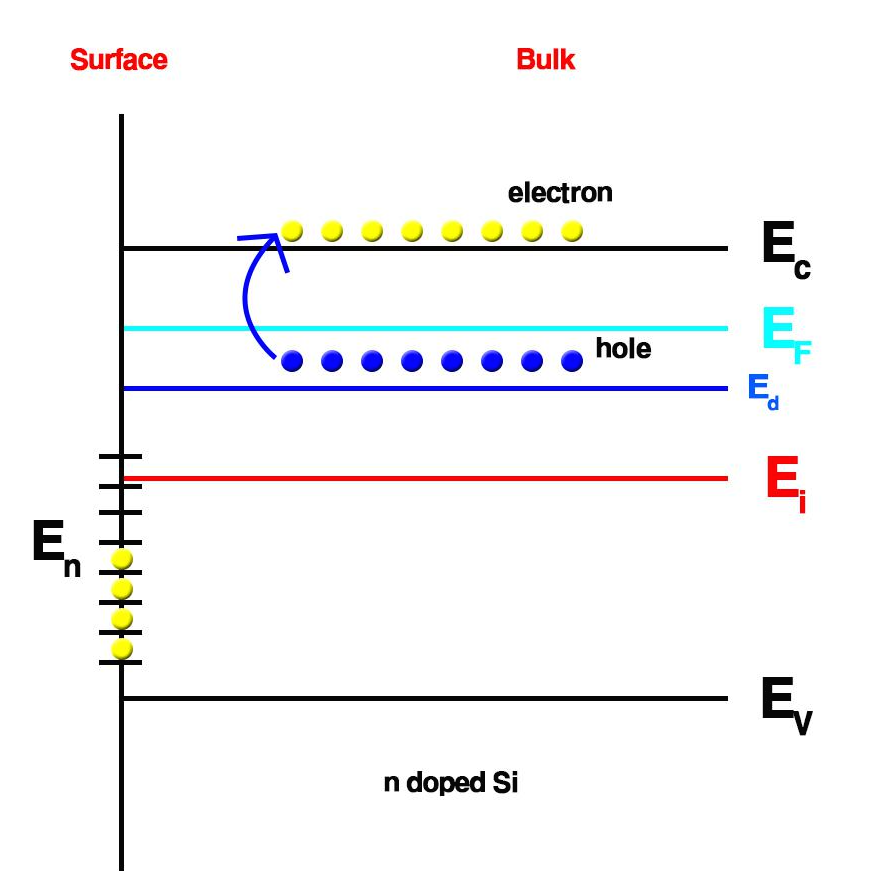

하지만 표면에는 bandgap 같은거 없습니다. 전자가 Ec와 Ev 사이에 있을 수 있어요. trap level에 있을 수 있어요.

그렇기 때문에 도핑된 전자들이 표면에 존재하는 trap level을 아래에서부터 채웁니다. 그러면 반대로 위쪽이 비어있겠죠? Fermi level은 +와 -의 사이에 존재합니다. 즉 전자가 마지막으로 채워진 trap level의 바로 윗 level이 표면의 fermi level입니다. 하지만 bulk의 Ef와 겹치잖아요. charge neutral level이라 새로 정의하고 En이라 표기합니다.

● 물질 내 평형 기준이 다르다? 기준을 맞춰야지!

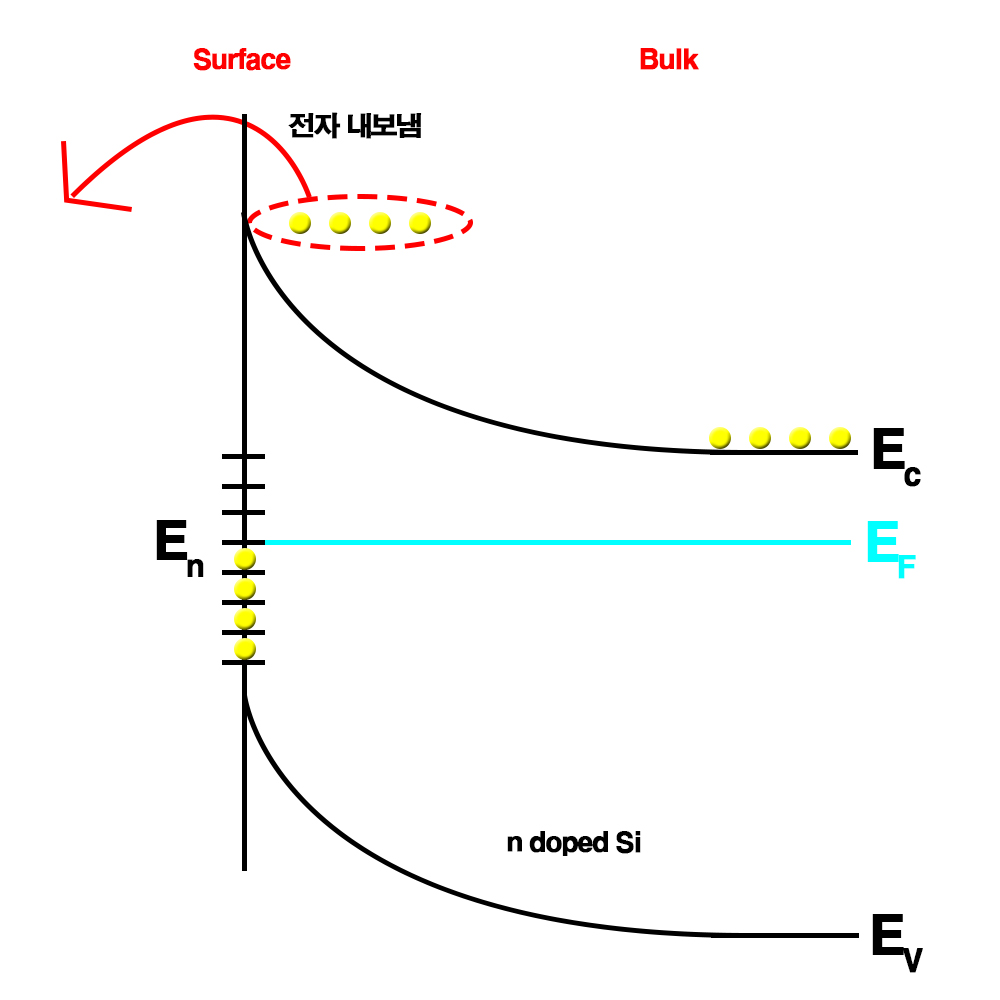

이렇게 봤을 경우 bulk 쪽의 fermi level Ef와 surface 쪽의 fermi level En이 달라지게 됩니다. 같은 물질인데도 equilibrium의 기준이 다른 것이죠. equilibrium의 기준을 맞추기 위해서, Fermi level을 맞추기 위해서 surface와 가까운 Bulk쪽의 전자가 surface 밖으로 이동하게 됩니다.

전자가 이동함에 따라 band는 아래로 휘게 되고, Ef와 En은 같은 높이에 위치하게 됩니다. 이 과정에서 bulk의 페르미 레벨은 무조건 surface의 charge neutral level에 고정되게 됩니다. pinning되게 됩니다. 그래서 이 현상을 fermi level pinning effect라고 부릅니다.

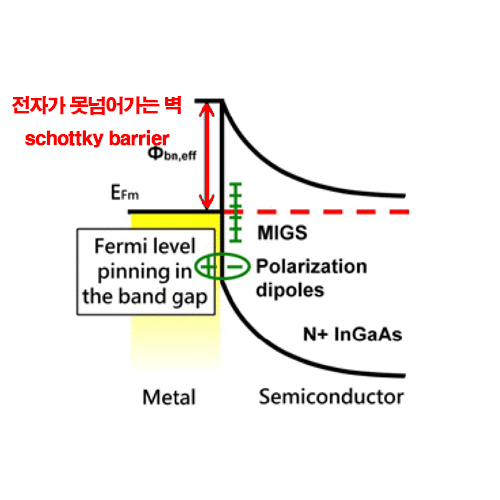

● metal과 semiconductor 접합시 생기는 schottky barrier

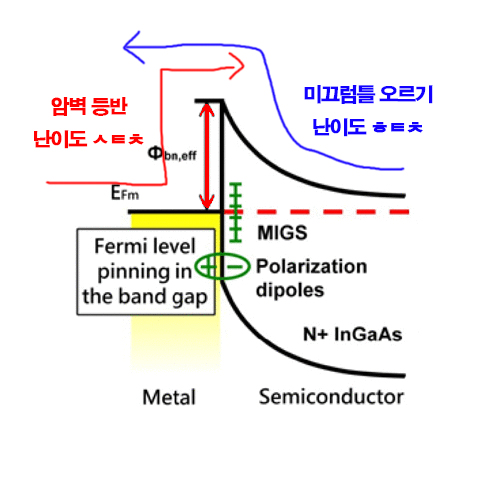

이게 뭐가 문제냐. 원래 반도체물질이랑 금속 물질이 접하면 barrier라는 벽이 생기긴 합니다. 이를 schottky barrier라고 합니다. 전자가 schottky barrier보다 더 큰 에너지를 가져야 넘어갈 수 있는 거예요.

위 그림을 보시면 silicon에서 metal로는 어찌저찌 전자가 넘어가요. 경사 완만해서 미끄럼틀 거꾸로 올라가는 것처럼 생겼잖아. 우리 미끄럼틀 거꾸로 올라갈 수 있잖아. 근데 metal에서 silicon으로 전자가 넘어갈 때 경사가 90도인 절벽, 쇼트키 배리어가 있죠? 못넘어갑니다. 전자 입장에서 암벽등반 하는거예요. 얼마나 힘들어.

결국 전류가 양방향으로 흐르지 못하는거죠. 자동차가 앞으로만 갈 수 있는거야. 후진을 못해. 쓸모 있어? 없어! But 이 벽의 높이를 낮춰서 양방향으로 흐르게 할 수 있어요. 'fermi level pinning이 발생하지 않았다면!'

● Fermi level pinning의 진정한 문제점

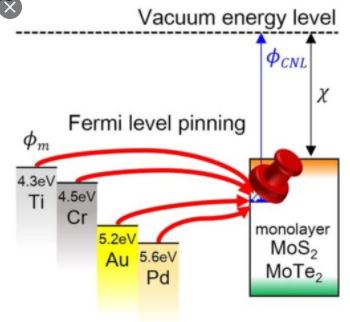

Fermi level pinning이 발생하지 않았다면, metal의 물질을 바꿔서(=work function이 다른 물질을 써서) schottky barrier을 낮출 수 있습니다. 벽의 높이는 metal의 work function과 관련있거든요. 전자가 metal에서 Si로 넘어가는데 느끼는 벽을 낮출 수 있는거야.

근데 Fermi level pinning이 발생할 경우 어떤 work function을 가진 metal이 오든 fermi level은 같은 곳에 고정되게 됩니다. 벽의 높이가 안낮아져. 항상 같은거야. 그 뜻은 전자가 항상 벽을 넘지 못하는거지.

결국 fermi level pinning은 소자를 무쓸모로 만듭니다. 자동차를 만들어놨더니 후진을 못하게 고장내는, 골치아픈 현상입니다. 이걸 방지해야 소자를 쓸모있게 할 수 있겠죠.

오늘 제가 준비한 포스팅은 여기까지구요. 긴 글 읽어주셔서 감사합니다~

'공대 대학원 생활 & 반도체 지식' 카테고리의 다른 글

| 돈을 목표로 석사, 박사학위를 딴다면 후회하겠지 (5) | 2020.11.23 |

|---|---|

| AFM(Atomic Force Microscope) 장비의 부품 이름들 tip같은거 (4) | 2020.11.14 |

| high k oxide 구조에서 Metal gate 쓰는 이유, poly depletion effect란? (47) | 2020.11.11 |

| GSAT 삼성 직무적성검사 온라인 시험본 후기 및 문제집 추천 (6) | 2020.11.01 |

| Gsat 삼성 직무적성검사 온라인 시험예비소집 후기 벌벌 떨린다 (6) | 2020.10.27 |